来源:半导体行业观察 |

发表时间:2018-12-04

点击:13055

昨天下午,从武汉新芯传来消息,该公司基于其三维集成技术平台的三片晶圆堆叠技术研发成功。

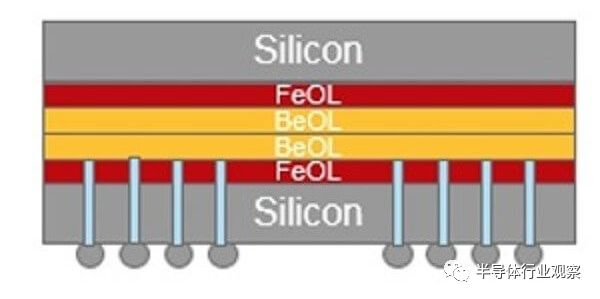

武汉新芯的晶圆级集成技术可将三片不同功能的晶圆(如逻辑、存储和传感器等)垂直键合,在不同晶圆金属层之间实现电性互连。与传统的2.5D芯片堆叠相比,晶圆级的三维集成技术能同时增加带宽、降低延时,并带来更高的性能与更低的功耗。

据悉,武汉新芯自2012年开始布局三维集成技术,并于2013年成功将三维集成技术应用于背照式影像传感器,良率高达99%,随后陆续推出硅通孔(TSV)堆叠技术、混合键合(Hybrid Bonding)技术和多片晶圆堆叠技术。

武汉新芯技术副总裁孙鹏表示:“三维集成技术是武汉新芯继NOR Flash、MCU之外的第三大技术平台,已积累了6年的大规模量产经验,能为客户提供工艺先进、设计灵活的晶圆级集成代工方案。”

三维异构集成技术

伴随着集成度和性能提升的迫切要求,集成电路的设计和制造、封装开始从平面向3D立体方向发展,并且逐步出现了不同结构芯片的集成。早期是多层多芯片集成,用于在单个衬底上横向集成不同类型半导体器件以及无源元件(包括滤波器和天线)。运用这种技术,无源元件被嵌入到多个层叠中以达到高Q值和小型化,同时,其中的短距互连能得到比传统印刷电路板技术更高的性能和集成度。

随着频率的上升,在多个集成电路间的互联块和线内的损耗迅速增加。同时多芯片集成通常缺乏几何和互联清晰度,以达成横向和纵向的紧密度。因此,人们开始研究各类新技术形式,用以克服互联的寄生效应,在这样的背景下,三维异构集成技术应运而生。

三维异构集成通常分为四个基本类别,分别是:单片(monolithic)、小芯片(chiplet)、晶圆键合(wafer-bonding)、和外延转移(epitaxial transfer)。而此次武汉新芯就是在晶圆键合技术上实现了突破。

在晶圆级异构集成(小芯片、晶圆键合和外延转移)方式中,硅与化合物半导体器件是在独立完成了各自工艺后集成的,这对现有的工艺制造过程构成的风险很小,并能在化合物半导体(如磷化铟)与硅(CMOS和BiCMOS)器件间提供紧密纵向集成。

其中,chiplet集成能将各种不同的半导体技术,例如氮化镓HEMT、磷化铟双HBT、以及硅MEMS等彼此相临地安放在一个完整的CMOS晶圆上。此种键合技术也打破了化合物半导体技术的芯片尺寸缩小障碍,因为III-V元素化合物chiplet能被放置于任意大小的CMOS晶圆上。

成熟还需要时间

实际上,这种3D的晶圆堆叠技术已有多年的研发历史,但技术成熟度还比较低,进入量产阶段仍需要一些时间,且相关技术主要被美国、韩国和中国台湾的先进半导体企业所把持,如三星、SK海力士、英特尔,以及台积电等,中国大陆的相关半导体企业这些年也在奋起直追,并一直在缩小与上述先进企业之间的差距,武汉新芯就是其中的代表企业。

谈到武汉新芯,就不能不说长江存储,因为武汉新芯是长江存储的子公司,二者的设计和制造技术,特别是存储器技术密不可分。

今年夏天,在美国举行的Flash Memory Summit峰会上,长江存储推出了Xtacking架构,这实际上也是一种3D的异构堆叠技术,虽然与此次武汉新芯推出的晶圆堆叠技术有所区别,但都同出一门,有着紧密的联系。

据悉,Xtacking架构将外围电路置于存储单元之上,从而实现比传统3D NAND更高的存储密度;其最大的特点是高速I/O,高存储密度,以及更短的产品上市周期。特别是在I/O速度方面,目前,世界上最快的3D NAND I/O速度的目标值是1.4Gbps,而大多数供应商仅能供应1.0 Gbps或更低的速度。利用Xtacking技术有望大幅提升NAND的I/O速度至3.0Gbps,这与DRAM DDR4的I/O速度相当。

长江存储已经把这项技术运用到相应的存储产品中(64层堆叠的),预计明年开始量产。

基于武汉新芯在IC设计方面多年的积累,长江存储的存储器设计和制造水平也在不断地迭代,特别是晶圆级堆叠技术的不断成熟,可以为其前沿存储器芯片的开发和制造添加砝码。

在晶圆级堆叠技术方面,大陆企业还处于追赶阶段,而在先进企业当中,三星、SK海力士、台积电等的技术进展最受瞩目,其中以台积电为最。

今年5月,台积电在美国举办的第24届年度技术研讨会上,发布了晶圆堆叠技术Wafer-on-Wafer(WoW),该技术通过使用形成硅通孔(TSV)连接的10微米孔彼此接触。按照台积电的合作伙伴Cadence的说法,堆叠晶圆设计可以放置在中介层上,将一个连接路由到另一个连接,创建一个双晶立方体,甚至可以使用WoW方法垂直堆叠两个以上的晶圆。

"

"

此前,台积电已经研发出了Chip on Wafer on Substrate(CoWoS)、Integrated Fan-Out (InFO)都是3D封装技术,这两种技术目前已经应用在多种产品上,比方说英特尔和Xilinx的FPGA芯片应用了CoWoS,苹果的A系列SoC应用了InFO。

据悉,新推出的WoW最大应用场景很可能是在GPU上,其可以在不增加GPU核心面积或者是使用更小工艺制程下增加晶体管数量,从而提升显卡性能。

不过,目前WoW技术的最大问题是对于工艺要求非常高,die之间要准确无误地对齐,而且要确保任何一片die都是没有问题的,否则组装完成后发现其中一个工作不了,整个封装完成的芯片就报废了,因此良品率比较低,生产成本较高。还有就是现在芯片的单位发热已经相当之高,采用堆叠技术的话会让发热更加集中,对芯片的寿命也难以控制。

因此,在已经非常成熟的16nm工艺上加入WoW比较妥当,但台积电的目标是在7nm和5nm制程上应用。

晶圆堆叠技术属于比较前沿的研究领域,类似于这种的三维集成技术是眼下业界的热门研发课题,但由于技术还不够成熟,因此量产还很少。

此次,武汉新芯实现了技术突破,是一个很喜人的消息,这使得人们对于长江存储明后年的新产品迭代更加期待了。

“本文由新材料在线®平台入驻媒体号半导体行业观察提供,观点仅代表作者本人,不代表本网站及新材料在线®立场,本站不对文章内容真实性、准确性等负责,尤其不对文中产品有关功能性、效果等提供担保。本站提醒读者,文章仅供学习参考,不构成任何投资及应用建议。如需转载,请联系原作者。如涉及作品内容、版权和其它问题,请与我们联系,我们将在第一时间处理!本站拥有对此声明的最终解释权。”