设置登录密码

*密码

*确认密码

完善信息

*真实姓名

*公司名称

*您的职位

城市

*邮箱

*主营产品

*行业

企业类型

材质

功能

来源:材料科技在线|

发表时间:2018-08-30

点击:14614

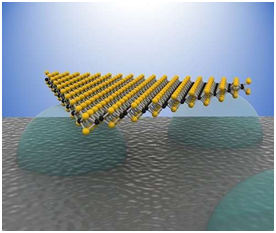

图1:穹顶结构的二维半导体的图像,图片来源:韩国科学技术研究院(KIST)

“本文由新材料在线®平台入驻媒体号材料科技在线提供,观点仅代表作者本人,不代表本网站及新材料在线®立场,本站不对文章内容真实性、准确性等负责,尤其不对文中产品有关功能性、效果等提供担保。本站提醒读者,文章仅供学习参考,不构成任何投资及应用建议。如需转载,请联系原作者。如涉及作品内容、版权和其它问题,请与我们联系,我们将在第一时间处理!本站拥有对此声明的最终解释权。”